Toshiba Memory Corporation desenvolve novo chip de ponte usando PAM 4 para aumentar a velocidade e capacidade de SSD

A Toshiba Memory Corporation, líder mundial em soluções de memória, anunciou hoje o desenvolvimento de um chip de ponte que faz com que unidades de estado sólido (SSDs, solid-state drives) alcancem alta velocidade e grande capacidade. Usando chips de ponte desenvolvidos com uma pequena área ocupada e baixo consumo de energia, a empresa foi bem-sucedida em conectar mais chips de memória flash com menos linhas de sinal de alta velocidade em comparação ao método convencional de chips sem ponte. Esse resultado foi anunciado no dia 20 de fevereiro em São Francisco, EUA, na International Solid-State Circuits Conference 2019 (ISSCC 2019).

Este comunicado de imprensa inclui multimédia. Veja o comunicado completo aqui: https://www.businesswire.com/news/home/20190221006060/pt/

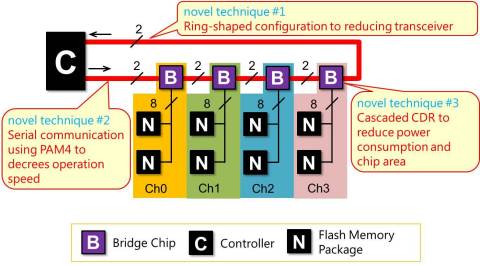

Fig. 1 Connection using bridge chips (Graphic: Business Wire)

Em SSDs, diversos chips de memória flash são conectados a um controlador que gerencia a sua operação. À medida que mais chips de memória são conectados a uma interface de controlador, a velocidade de operação diminui, e há limites ao número de chips que podem ser conectados. Para aumentar a capacidade, é necessário aumentar o número de interfaces, mas isso resulta em um grande número de linhas de sinal de alta velocidade conectadas ao controlador, dificultando a implementação da fiação na placa da SSD.

A empresa resolveu esse problema com o desenvolvimento de um chip de ponte que conecta o controlador e os chips de memória flash (Fig. 1) por meio de três técnicas novas: uma conexão em margarida (daisy chain)*1, que inclui o controlador e os chips de ponte em forma de anel; uma comunicação em série usando PAM 4*2; e uma técnica de melhoria de jitter (tremulação)*3 para eliminar um circuito PLL*4 nos chips de ponte. Ao usar essas técnicas, a sobrecarga dos chips de ponte é reduzida, e é possível operar um grande número de chips de memória flash a uma alta velocidade apenas com algumas linhas de sinal (Fig. 2) de alta velocidade.

A configuração em forma de anel dos chips de ponte e do controlador reduz o número de transceptores necessários no chip de ponte de dois pares para um par, alcançando a redução da área do chip de ponte. Além disso, adotar uma comunicação em série PAM 4 entre o controlador e os chips de ponte em margarida reduz a velocidade de operação nos circuitos dos chips de ponte e o desempenho exigido. Uma nova CDR*5, que usa as características de PAM 4 para melhorar as características de jitter, elimina a necessidade de um circuito PLL no chip de ponte, o que também contribui para uma área menor do chip e um consumo de energia reduzido.

Os chips de ponte em versão protótipo foram fabricados com processo CMOS de 28nm, e os resultados foram avaliados ao conectar quatro chips de ponte e um controlador em margarida em forma de anel. Isso confirmou o desempenho satisfatório da comunicação PAM 4 por todos os chips de ponte e controlador a 25.6 Gbps, e também que é possível obter uma BER*6 inferior a 10-12.

No futuro, a empresa continuará o trabalho de desenvolvimento com a meta de alcançar armazenamento de grande capacidade a alta velocidade em níveis jamais vistos, ao aprimorar ainda mais o desempenho dos chips de ponte, reduzindo sua área e seu consumo de energia.

Observações

*1 Conexão em margarida (daisy chain): um esquema de conexões onde diversos chips estão conectados em sequência

*2 PAM 4: modulação de amplitude de pulso com 4 níveis (contém dados com 4 valores)

*3 Jitter: flutuação no domínio de tempo de formas de onda de sinal ou relógio

*4 PLL: laço fechado por fase (um circuito que gera um sinal de referência correto)

*5 CDR: recuperação de dados e relógio (um circuito que recupera os dados e o relógio a partir do sinal recebido)

*6 BER: taxa de bits errados (quanto menor for o valor, melhor será o desempenho)

Sobre a Toshiba Memory Corporation

A Toshiba Memory Corporation, líder mundial em soluções de memória, dedica-se ao desenvolvimento,àprodução e às vendas de memória flash e SSDs. Em junho de 2018, a Toshiba Memory foi adquirida por um consórcio industrial liderado pela Bain Capital. A Toshiba Memory é pioneira em soluções e serviços de memória flash de ponta que enriquecem a vida das pessoas e ampliam os horizontes da sociedade. A tecnologia inovadora de memória flash em 3D da empresa, a BiCS FLASH™, está moldando o futuro da armazenagem em aplicativos de alta densidade, incluindo smartphones avançados, PCs, SSDs, automotivos e centros de dados. Para obter mais informação sobre a Toshiba Memory, acesse https://business.toshiba-memory.com/en-apac/top.html

O texto no idioma original deste anúncio é a versão oficial autorizada. As traduções são fornecidas apenas como uma facilidade e devem se referir ao texto no idioma original, que é a única versão do texto que tem efeito legal.

Ver a versão original em businesswire.com: https://www.businesswire.com/news/home/20190221006060/pt/

Contato:

Toshiba Memory Corporation

Kota Yamaji

Divisão de planejamento de negócios

Telefone: +81-3-6478-2319

semicon-NR-mailbox@ml.toshiba.co.jp

Fonte: BUSINESS WIRE